# Vol. 2, No. 1, 2012

# LINEAR-MODE OPERATION OF A HIGH-ORDER SINGLE-BIT SIGMA-DELTA MODULATOR

## Roman Kochan

Lviv Polytechnic National University kochan.roman@gmail.com

**Abstract:** This paper considers a simulation mathematical model of a high-order single-bit sigmadelta modulator. Both the condition and the criterion of this modulator operation in a linear mode have been formulated.

**Key words:** high-order sigma-delta modulator, linear-mode operation, simulation model.

#### 1. Introduction

The sigma-delta modulators (SDM) are the base of most precision analog to digital converters (ADC) at the present time [1, 2]. Usually SDMs are divided to singleor malty- bit according to the capacity of output code [3]. The precision ADCs are usually based on single bit SDM [4, 5]. The single bit SDMs are divided to first-... order according to the number of feedback loops.

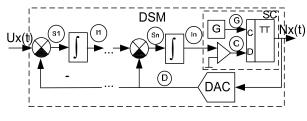

The structure of single bit high order SDM is presented on fig. 1. Its forward signal's line consists of the set of summators O, the set of integrators  $\fbox{I}$  and synchronous comparator SC, which consists of asynchronous comparator and synchronous D- trigger TT. The feedback loop consists of single bit digital to analog converter DAC controlled by output code of SDM. The trigger TT is synchronized by pulse generator G. The most impotent points of the SDM are signed by letters in the circle. The output code of SDM – Nx(t).

Fig. 1. Structure of a high- order single- bit SDM

The investigation of high order SDM [6] detected the problem of SDM operation in linear operating mode for input signals changing in wide dynamic range. The linear operation mode of SDM here we mean as linear operation mode of ADC based on SDM. This mode is in the condition when increasing (decreasing) of input analog voltage of SDM brings proportional increasing (decreasing) of result ща analog to digital conversion. It is caused by the fact if output signal of some integrator exceed feedback signal the next integrator can not discharge. It is because this next integrator continues integration the same polarity signal that it was in the previous cycle. So the direction of moving of output signal of this integrator is not changed and integrator comes to saturation. It breaks the forward signal's line and fixes the output code of SDM. So the main objective of this work is in investigation of conditions of absence the described effect and providing the stable operation of high order SDM in linear operation mode.

According to the traditional conception of stability of discrete systems [7] "the limited output signal in the condition of limited input signal" the SDM is always stable because its output signal has limited number of conditions. So the indicated before condition of stability is always true. The analisys of leterature [3, 8] show that problem of providing linear operation mode for high order SDM is not indicated and it does not allow us to develop SDM, which operates in wide dynamik range.

## 2. Simulation model of high-order single-bit SDM

The sensitive points of SDM are marked by letters in circles in Fig.1. The voltage dependences of time t for these points can be described by a components equation of a simulation model of n-order SDM. The topology equation of the linear simulation model of n-order SDM (for  $n \ge 2$ ) can be described by the following system of equations

$$\begin{cases} U_{G}(t) = \begin{cases} 1, t \in [k \times T, (k+0,5) \times T] \\ 0, t \in ((k+0,5) \times T, (k+1) \times T) \end{cases} \\ U_{C}(t) = \begin{cases} 1, U_{In}(t) > 0 \\ 0, U_{In}(t) \le 0 \end{cases} \\ U_{S1}(t) = U_{X}(t) - U_{D}(t) \\ U_{Ii}(t) = \frac{1}{\tau_{i}} \int_{0}^{t} U_{Si}(t) dt; i = \overline{1, n} \end{cases} \\ U_{Si}(t) = U_{I(i-1)}(t) - U_{D}(t); i = \overline{2, n} \\ N_{X}(t) = \begin{cases} U_{C}(t), (U_{G}(t) = 1) \land (U_{G}(t - \Delta t) = 0) \\ N_{X}(t - \Delta t) \end{cases} \\ U_{D}(t) = \begin{cases} E, N_{X}(t) = 1 \\ -E, N_{X}(t) = 0 \end{cases} \end{cases}$$

(1)

where:  $U_X$  is the input voltage;  $N_X$  is the output code, which corresponds to  $U_X$ ;  $U_{S1}...U_{Sn}, U_{I1}...$  $...U_{In}, U_C, U_G, U_D$  are the voltages of the appropriate points of SDM;  $\tau$  is the integrator time constant; T is the pulse generator period; k is the integer value;  $\Delta t \rightarrow 0$  is the time step of modelling; E is the output voltage of DAC.

### 3. Linear-mode operation

The condition of n-order SDM operation in the linear mode can be presented as

$$U_{I_{MAX_i}} < E, i = \overline{1, n-1} \qquad ,$$

where:  $U_{IMAX_i}$  is the maximum allowable output voltage of i-th integrator, which is achieved at the end of the integrating pulse when the output voltage of the previous integrator, or the input voltage for the first integrator, is maximum and of opposite polarity to the DAC's output voltage. This condition may be presented as follows

$$\begin{cases} U_{X} = U_{XMAX} > 0 \\ U_{D} = -E \\ U_{I1}(t) = \frac{1}{\tau_{1}} \int_{0}^{t} (U_{XMAX} + E) dt < E \\ U_{Ii}(t) = \frac{1}{\tau_{i}} \int_{0}^{t} (U_{Ii-1} + E) dt < E; i = \overline{2, n-1} \end{cases}$$

(2)

where  $U_{X MAX}$  is the maximum allowable input voltage for the linear operating mode of SDM.

The integrals of (2) we can present as

$$\int_{0}^{t} f(t)dt = \int_{t-T}^{t} f(t)dt + C; \quad C = \int_{0}^{t-T} f(t)dt \quad . \quad (3)$$

When we take (3) into consideration we can present (2) in such form

$$\begin{cases} U_{IMAX_{1}} = \frac{1}{\tau_{1}} (U_{XMAX} + E)T + C_{1} < E \\ U_{IMAX_{2}} = \frac{1}{\tau_{2}} \frac{1}{\tau_{1}} (U_{XMAX} + E) \frac{T^{2}}{2} + \frac{1}{\tau_{2}} (C_{1} + E)T + C_{2} < E \\ U_{IMAX_{n-1}} = \prod_{i=1}^{n-1} \frac{1}{\tau_{i}} (U_{XMAX} + E) \frac{T^{n-1}}{(n-1)!} + \prod_{i=2}^{n-1} \frac{1}{\tau_{i}} (C_{1} + E) \times \\ \times \frac{T^{n-2}}{(n-2)!} + \dots + (C_{n-2} + E)T + C_{n-1} < E \end{cases}$$

where  $C_1...C_{n-1}$  is the output voltage of an appropriate integrator at the beginning of an integration cycle.

In the steady-state operation conditions the output voltages of all integrators are periodic signals with a volt-second area of charging pulses equal to an area of recharging pulses and the average value of this voltage equal to the input voltage of SDM. So, the output voltage of each integrator is not more than the input voltage at the beginning of a charging cycle

$$C_i \le U_{X MAX}, i = 1, n - 1$$

. (4)

Therefore, the condition of linear operating mode we can present as

$$\sum_{i=1}^{m} \left( \frac{T^{m-i+1}}{(m-i+1)!} \prod_{j=i}^{m} \frac{1}{\tau_{j}} \right) < \frac{1-K}{1+K}; m = \overline{1, n-1} \quad , \quad (5)$$

where  $K = \frac{U_{X MAX}}{E}$

At the same time the output signal of the last (n-th) integrator can be varied in the range [0, E]. This allows us to decrease the influence of comparator's parameters on ADC's error. We can present this condition so:

$$U_{In}(t) = \frac{1}{\tau_n} \int_0^t (U_{In-1} + E) dt < E \quad . \tag{6}$$

Taking into consideration (3) and (2) we can present (6) in the form

$$\tau_n > 2T \qquad . \tag{7}$$

## 4. Computation of SDM's parameters

The computed parameters of 6-th order SDM are presented in Table 1 for the frequency of pulse generator 100 kHz (T=10  $\mu$ S) and output voltage of DAC ± 5 V.

Table 1

Parameters of SDM

|             | $U_{X MAX} = 2,5$ | $U_{X MAX} = 3,5$ | $U_{X MAX} = 4,5$ |

|-------------|-------------------|-------------------|-------------------|

| $1/	au_1$   | 3,33E+04          | 1,76E+04          | 5,26E+03          |

| $1/\tau_2$  | 2,86E+04          | 1,62E+04          | 5,13E+03          |

| $1/\tau_3$  | 2,88E+04          | 1,63E+04          | 5,13E+03          |

| $1/	au_4$   | 2,88E+04          | 1,63E+04          | 5,13E+03          |

| $1/	au_{5}$ | 2,88E+04          | 1,63E+04          | 5,13E+03          |

| $1/\tau_6$  | 5,00E+04          | 5,00E+04          | 5,00E+04          |

As we can see in Table 1 and (7) the time constant of the last integrator depends only on the parameters of the pulse generator. The integrators' time constant beginning from the third integrator, or even beginning from the second one for the case  $U_{XMAX} = 4,5 V$ , is a constant value and does not depend on the number of integrators. It can be explained by greater influence of the factorial function in the denominator of (5) in comparison with the power function in the numerator. So, we can build SDM of arbitrary order using three or four types of integrators. The time constant of these integrators can be computed according to (5) and (7).

#### 5. Experimental research

It has been proposed to investigate the obtained results by investigating oscillogrames of signals in the appropriate points of SDM with the integrators whose parameters correspond to Table 1. The investigation has been done using the simulation model of SDM described in [6, 9]. The signal oscillogrames of second order SDM are presented in Fig. 2. The curves of the output signal of the integrators are marked by symbols: "o" - for the first integrator (a blue line) and "+" - for the second integrator (a black line). These graphs have been constructed for the cases  $U_x = U_{XMAX} = 2,5 V$  and  $U_{X} = U_{XMAX} = 3,5 V (U_{X} \text{ marked by a red line})$ using the symbol "\*"). Changing the output signal of a synchronous comparator (signal  $N_x(t)$  is marked by a polygonal green line using the symbol "\$") causes changing the direction of output signal for all integrators. As we can see in Fig. 2 the output signals of all integrators do not exceed the output voltage of the feedback DAC, therefore, the condition (2) is fulfilled for these cases. Besides, the output signal of the first integrator may be increased to higher values limited by some range because we consider inequality (4) for the worst case. It brings some increase in the real range of the input signal for the linear mode in comparison with the predefined one.

Fig. 2. Oscillogrames of second order SDM

The oscillogrames of the third order SDM signals are presented in Fig. 3. The curves of the output signal of the integrators are marked by symbols: "o" - for the first integrator (a blue line), "+" – for the second and "\$" – for the third (black lines). These graphs have been also constructed for the same cases  $U_x = U_{XMAX} = 2,5 V$ and  $U_X = U_{XMAX} = 3,5 V$  ( $U_X$  marked by a red line using the symbol "\*"). Similarly as it has been observed for the second order SDM, changing the output signal of a synchronous comparator (signal  $N_{x}(t)$  is marked by a polygonal green line using the symbol «◊») causes changing the direction of output signal for all integrators. As we can see in Fig. 3 the output signals of all integrators also do not exceed the output voltage of the feedback DAC, therefore, the condition (2) is fulfilled for these cases, too. And as it has been for the second order SDM we also have some reserve for the output signal for the second and third integrators. It will also bring increasing the range of input signal for the linear mode of the whole SDM.

Fig. 3. Oscillogrames of third order SDM

Simulation of a higher-order SDM proves selfoscillating of integrator's output signals. These oscillations could be explained by transformation of the negative feedback to a positive one when we have four and more series-connected integrators. This problem can be solved by introducing nonlinear components or nonlinear connection into the structure of the higherorder SDM or by changing the structure of SDM to highorder cascade [3], which includes a set of series-parallel connected first-, second- or third- order sub-modulators.

#### 6. Conclusions

Therefore, there has been conducted the analysis of the simulation mathematical model of a high-order single-bit sigma-delta modulator which allows us to formulate the condition and to obtain the criterion of its operation in the linear mode. Also the presented apparatus enables to compute the parameters of integrators for SDM, which operates in the linear operating mode for the defined range of input signals. The simulation of second and third order SDM operation confirms the linear mode for input signal changing in the predefined range for parameters of SDM computed by the presented methodology.

#### References

1. Kester W. Which ADC Architecture Is Right for Your Application // Analog Dialogue. – 2005. – Vol. 39, № 2. – P.11-19. http://www.analog.com/library/ analogdialogue/archives/39-06/architecture.pdf

2. Fowler K. Part 7: analog-to-digital conversion in real-time systems // IEEE Instrumentation & Measurement Magazine. –2003. – Vol. 6. No. 3. –P. 58-64.

3. Medeiro F., Pérez-Verdú A., Rodríguez-Vázquez A. Top-Down Design of High-Performance Sigma-Delta Modulators // The Springer International Series in Engineering and Computer Science. Kluwer Academic Pub. – 1999. –287 p.

4. Kester W. Data Conversion Handbook. ISBN 0750678410. – 2004. –953 p.

5. Golub V. Sigma-Delta Modulators and analog to digital converters // Technology and Design in Electronic Devices. – 2003.– № 4. –P. 35 – 41. [Rus]

6. Kochan R. Influence of Integrator's Parameters on Nonlinearity of High Order Sigma-Delta Modulator // Acquisition and Processing of Information. – 2010. – No. 33(109). – Pp. 52 – 59. [Ukr]

7. Kuzin L. Computing and developing of discrete control systems. – M: State scientific & technical publish house of manufacturing literature. – 1962. –684p. [Rus]

8. Schreier R., Temes G. Understanding Delta-Sigma Data Converters. – John Wiley & Sons, New York. –2004. – 455 p.

9. Kochan R., Klym H. Simulation Model of Delta-Sigma Modulator// Proc. of X-th International Conference «Modern problems of radio engineering, telecommunications and computer science» TCSET'2010. – 2010.–P. 44.

# ЛІНІЙНИЙ РЕЖИМ РОБОТИ ОДНОБІТНОГО СИГМА-ДЕЛЬТА МОДУЛЯТОРА ВИСОКОГО ПОРЯДКУ

# Р. Кочан

Розглянуто імітаційну математичну модель однобітного сигма-дельта модулятора високого порядку.

Сформульовано умову та критерій роботи цього модулятора в лінійному режимі.

Roman Kochan – Ph.D. in information measurement systems, an associate professor of Specialized Computer Systems Department. Research interests: DAQ System and Network, Intelligent Measurement Systems.